It has been a while since I wrote something on my site, but I haven't been sitting doing nothing in the meantime....

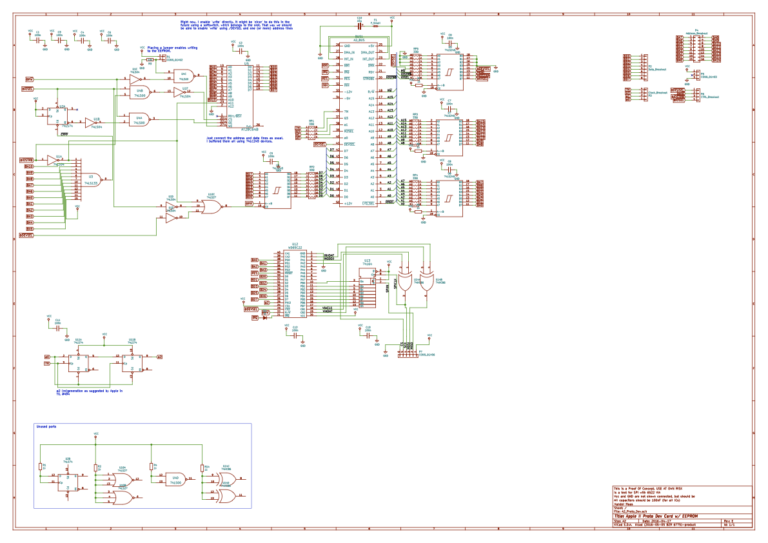

As mentioned in one of my blog posts, I made another revision of my card, so I can continue my exploration of the Apple ][, hardware-wise.

My goal will be to have an SPI bus on my IIgs. After some Googling, I found a nice idea/implementation by André Fachat on 6502.org (André's 8-bit pages), who has make an SPI implementation with the 6522 VIA, with bit-banging, the other using PHI2.

I extended my circuit to incorporate the 6522, including a 74HCT74 to re-create the PHI2 clock, which is missing on the Apple ][ bus. I use a 65SC22, which should have some bugs resolved.

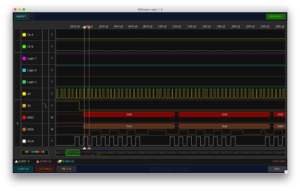

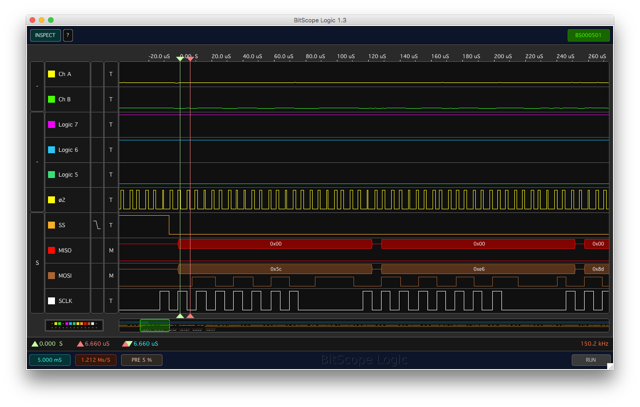

I also rewrote the driver André made for his CS/A65 computer for ca65 as I write my code in Xcode IDE. Testing the code, I didn't get the results I expected, so I got my Bitscope micro and fired up Bitscope Logic to sniff the SPI bus. You can find the code here..

Somehow it seems the SCLK signal is out-of-sync with the MOSI/MISO signal(s), in the screenshot I was sending $aa to the SPI bus. Right now I am out of ideas for this route. I might go the CPLD way (also an implementation by André)